# Nonvolatile Memory, Dual 1024-Position Programmable Resistors

ADN2850\*

#### **FEATURES**

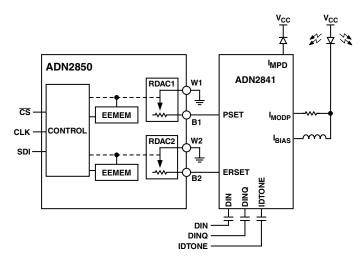

Dual, 1024-Position Resolution  $25~k\Omega$ , 250  $k\Omega$  Full-Scale Resistance Low Temperature Coefficient: 35 ppm/°C Nonvolatile Memory¹ Preset Maintains Wiper Settings Permanent Memory Write-Protection Wiper Settings Read Back Actual Tolerance Stored in EEMEM¹ Linear Increment/Decrement Log Taper Increment/Decrement SPI Compatible Serial Interface 3 V to 5 V Single Supply or  $\pm 2.5$  V Dual Supply 26 Bytes User Nonvolatile Memory for Constant Storage Current Monitoring Configurable Function 100-Year Typical Data Retention  $T_A = 55^{\circ}C$

#### **APPLICATIONS**

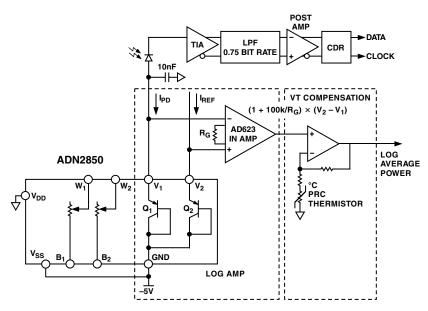

SONET, SDH, ATM, Gigabit Ethernet, DWDM Laser Diode Driver Optical Supervisory Systems

#### **GENERAL DESCRIPTION**

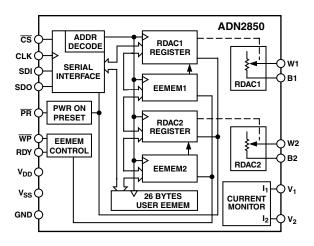

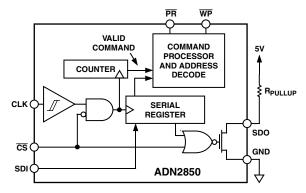

The ADN2850 provides dual-channel, digitally controlled programmable resistors<sup>2</sup> with resolution of 1024 positions. These devices perform the same electronic adjustment function as a mechanical rheostat with enhanced resolution, solid-state reliability, and superior low temperature coefficient performance. The ADN2850's versatile programming via a standard serial interface allows 16 modes of operation and adjustment, including scratch pad programming, memory storing and retrieving, increment/decrement, log taper adjustment, wiper setting readback, and extra user defined EEMEM<sup>1</sup>.

Another key feature of the ADN2850 is that the actual tolerance is stored in the EEMEM. The actual full-scale resistance can therefore be known, which is valuable for tolerance matching and calibration.

In the scratch pad programming mode, a specific setting can be programmed directly to the RDAC<sup>2</sup> register, which sets the resistance between terminals W and B. The RDAC register can also be loaded with a value previously stored in the EEMEM register. The value in the EEMEM can be changed or protected. When changes are made to the RDAC register, the value of the new setting can be saved into the EEMEM. Thereafter, such value will be transferred automatically to the RDAC register during system power ON, which is enabled by the internal preset strobe. EEMEM can also be retrieved through direct programming and external preset pin control.

\*Patent pending

NOTES

<sup>1</sup>The term nonvolatile memory and EEMEM are used interchangeably.

<sup>2</sup>The term programmable resistor and RDAC are used interchangeably.

#### REV. B

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

#### FUNCTIONAL BLOCK DIAGRAM

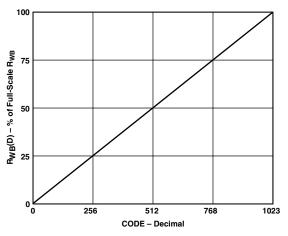

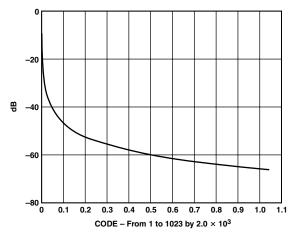

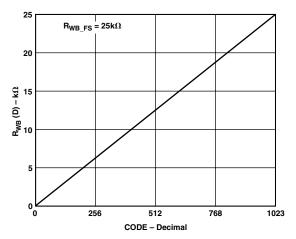

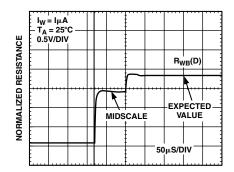

Figure 1. R<sub>WB</sub>(D) vs. Decimal Code

The linear step increment and decrement commands enable the setting in the RDAC register to be moved UP or DOWN, one step at a time. For logarithmic changes in wiper setting, a left/right bit shift command adjusts the level in  $\pm 6$  dB steps.

The ADN2850 is available in the 5 mm  $\times$  5 mm 16-lead frame chip scale LFCSP and thin 16-lead TSSOP packages. All parts are guaranteed to operate over the extended industrial temperature range of  $-40^{\circ}$ C to  $+85^{\circ}$ C.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 www.analog.com

Fax: 781/326-8703 © Analog Devices, Inc., 2002

# ADN2850-SPECIFICATIONS

#

| Parameter                                       | Symbol                     | Conditions                                                                       | Min        | $Typ^2$ | Max               | Unit               |

|-------------------------------------------------|----------------------------|----------------------------------------------------------------------------------|------------|---------|-------------------|--------------------|

| DC CHARACTERISTICS RHEOSTAT                     | MODE (Spe                  | ecifications apply to all RDACs)                                                 |            |         |                   |                    |

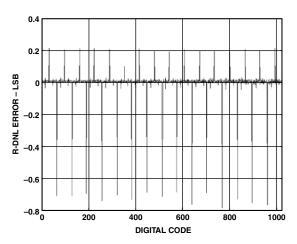

| Resistor Differential Nonlinearity <sup>3</sup> | R-DNL                      | $ R_{\mathrm{WB}} $                                                              | -2         |         | +2                | LSB                |

| Resistor Integral Nonlinearity <sup>3</sup>     | R-INL                      | $R_{WB}$                                                                         | -4         |         | +4                | LSB                |

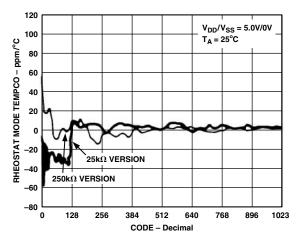

| Resistance Temperature Coefficient              | $\Delta R_{WB}/\Delta_{T}$ | "3                                                                               |            | 35      |                   | ppm/°C             |

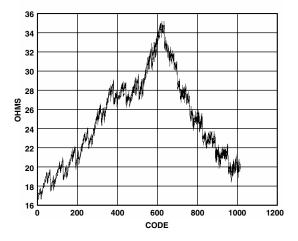

| Wiper Resistance                                | R <sub>W</sub>             | $V_{\rm DD} = 5 \text{ V}, I_{\rm W} = 100 \mu\text{A},$                         |            |         |                   | **                 |

| r                                               | "                          | Code = Half-scale                                                                |            | 50      | 100               | Ω                  |

|                                                 |                            | $V_{\rm DD} = 3 \text{ V}, I_{\rm W} = 100 \mu\text{A},$                         |            |         |                   |                    |

|                                                 |                            | Code = Half-scale                                                                |            | 200     |                   | Ω                  |

| Channel Resistance Matching                     | $\Delta R_{WB}/R_{WB}$     | Ch 1 and 2 $R_{WB}$ , $Dx = 3FF_H$                                               |            | 0.1     |                   | %                  |

| Nominal Resistor Tolerance                      | $\Delta R_{\mathrm{WB}}$   | WB5                                                                              | -30        |         | +30               | %                  |

|                                                 | WB                         |                                                                                  |            |         |                   |                    |

| RESISTOR TERMINALS                              | 37                         |                                                                                  | <b>3</b> 7 |         | <b>T</b> 7        | 3.7                |

| Terminal Voltage Range <sup>4</sup>             | $V_{W, B}$                 | C-1 MIL 1. CMD                                                                   | $V_{SS}$   |         | $V_{\mathrm{DD}}$ | V                  |

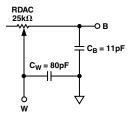

| Capacitance <sup>5</sup> Bx                     | $C_B$                      | f = 1 MHz, measured to GND,                                                      |            |         |                   |                    |

| 5 W/                                            |                            | Code = Half-scale                                                                |            | 11      |                   | pF                 |

| Capacitance <sup>5</sup> Wx                     | $C_{W}$                    | f = 1 MHz, measured to GND,                                                      |            | 0.0     |                   |                    |

|                                                 | _                          | Code = Half-scale                                                                |            | 80      |                   | pF                 |

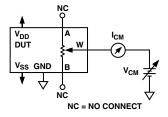

| Common-Mode Leakage Current <sup>6</sup>        | $I_{CM}$                   | $V_{\rm W} = V_{\rm B} = V_{\rm DD}/2$                                           |            | 0.01    | ±2                | μA                 |

| DIGITAL INPUTS AND OUTPUTS                      |                            |                                                                                  |            |         |                   |                    |

| Input Logic High                                | $V_{IH}$                   | With respect to GND, $V_{DD} = 5 \text{ V}$                                      | 2.4        |         |                   | V                  |

| Input Logic Low                                 | $V_{IL}$                   | With respect to GND, $V_{DD} = 5 \text{ V}$                                      |            |         | 0.8               | V                  |

| Input Logic High                                | $V_{IH}$                   | With respect to GND, $V_{DD} = 3 \text{ V}$                                      | 2.1        |         |                   | V                  |

| Input Logic Low                                 | $V_{IL}$                   | With respect to GND, $V_{DD} = 3 \text{ V}$                                      |            |         | 0.6               | V                  |

| Input Logic High                                | $V_{IH}$                   | With respect to GND,                                                             |            |         |                   |                    |

|                                                 | 111                        | $V_{DD} = +2.5 \text{ V}, V_{SS} = -2.5 \text{ V}$                               | 2.0        |         |                   | V                  |

| Input Logic Low                                 | $V_{IL}$                   | With respect to GND,                                                             |            |         |                   |                    |

| 1                                               | l IL                       | $V_{DD} = +2.5 \text{ V}, V_{SS} = -2.5 \text{ V}$                               |            |         | 0.5               | V                  |

| Output Logic High (SDO, RDY)                    | $V_{OH}$                   | $R_{PULL-UP} = 2.2 \text{ k}\Omega \text{ to 5 V}$                               | 4.9        |         |                   | V                  |

| Output Logic Low                                | V <sub>OL</sub>            | $I_{OL} = 1.6 \text{ mA}, V_{LOGIC} = 5 \text{ V}$                               |            |         | 0.4               | V                  |

| Input Current                                   | I <sub>IL</sub>            | $V_{IN} = 0 \text{ V or } V_{DD}$                                                |            |         | ±2.25             | μA                 |

| Input Capacitance <sup>5</sup>                  | C <sub>IL</sub>            | · IN · · · · · · · · · · · · · · · · · ·                                         |            | 5       |                   | pF                 |

| <del></del>                                     | 112                        |                                                                                  |            |         |                   | 1                  |

| POWER SUPPLIES                                  | ***                        | X - OX                                                                           | 2.0        |         |                   | ***                |

| Single-Supply Power Range                       | $V_{DD}$                   | $V_{SS} = 0 V$                                                                   | 3.0        |         | 5.5               | V                  |

| Dual-Supply Power Range                         | $V_{\rm DD}/V_{\rm SS}$    | W - W - CND                                                                      | ±2.25      |         | $\pm 2.75$        | V                  |

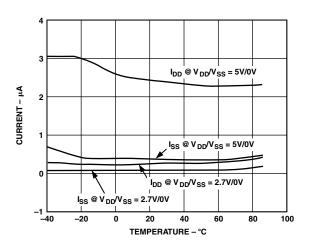

| Positive Supply Current                         | $I_{DD}$                   | $V_{IH} = V_{DD}$ or $V_{IL} = GND$ ,                                            |            | 2       | 4.5               |                    |

| D :: 0 1 0                                      | _                          | $T_A = 25^{\circ}C$                                                              |            | 2       | 4.5               | μA                 |

| Positive Supply Current                         | $I_{DD}$                   | $V_{IH} = V_{DD}$ or $V_{IL} = GND$                                              |            | 3.5     | 6.0               | μΑ                 |

| Programming Mode Current                        | $I_{\mathrm{DD(PG)}}$      | $V_{IH} = V_{DD}$ or $V_{IL} = GND$                                              | 2          | 35      | •                 | mA                 |

| Read Mode Current <sup>7</sup>                  | $I_{\text{DD(XFR)}}$       | $V_{IH} = V_{DD}$ or $V_{IL} = GND$                                              | 0.3        | 3       | 9                 | mA                 |

| Negative Supply Current                         | $I_{SS}$                   | $V_{IH} = V_{DD}$ or $V_{IL} = GND$ ,                                            |            | a =     |                   |                    |

| D D: : : °                                      | _                          | $V_{DD} = +2.5 \text{ V}, V_{SS} = -2.5 \text{ V}$                               |            | 3.5     | 6.0               | μA                 |

| Power Dissipation <sup>8</sup>                  | P <sub>DISS</sub>          | $V_{IH} = V_{DD}$ or $V_{IL} = GND$                                              |            | 18      | 50                | μW                 |

| Power Supply Sensitivity                        | P <sub>SS</sub>            | $\Delta V_{\rm DD}$ = 5 V ± 10%                                                  |            | 0.002   | 0.01              | %/%                |

| CURRENT MONITOR TERMINALS                       |                            |                                                                                  |            |         |                   |                    |

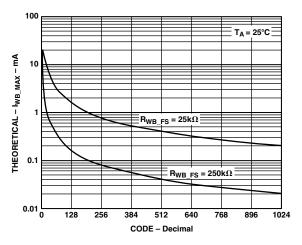

| Current Sink at V <sub>1</sub> <sup>9</sup>     | $I_1$                      |                                                                                  | 0.0001     |         | 10                | mA                 |

| Current Sink at V <sub>2</sub>                  | $I_2$                      |                                                                                  |            |         | 10                | mA                 |

|                                                 | 1                          |                                                                                  |            |         |                   |                    |

| DYNAMIC CHARACTERISTICS <sup>5, 10</sup>        |                            | D - 25 h0/250 h0 f = 1 htt-                                                      |            | 20/64   |                   | nV/√ <del>Hz</del> |

| Resistor Noise Spectral Density                 | e <sub>N_WB</sub>          | $R_{WB\_FS} = 25 \text{ k}\Omega/250 \text{ k}\Omega, \text{ f} = 1 \text{ kHz}$ |            | 20/64   |                   | II V / V IIZ       |

| Analog Crosstalk ( $C_{W1}/C_{W2}$ )            | $C_{\mathrm{T}}$           | $V_{B1} = V_{B2} = 0$ V, Measured $V_{W1}$ with                                  |            |         |                   |                    |

|                                                 |                            | $V_{W2} = 100 \text{ mV p-p} @ f = 100 \text{ kHz},$                             |            | <i></i> |                   | 170                |

|                                                 |                            | Code 1 = Code 2 = $200_{H}$                                                      |            | -65     |                   | dB                 |

REV. B -2-

| Parameter                                                                | Symbol             | Conditions                                                   | Min | Typ <sup>2</sup> | Max | Unit             |

|--------------------------------------------------------------------------|--------------------|--------------------------------------------------------------|-----|------------------|-----|------------------|

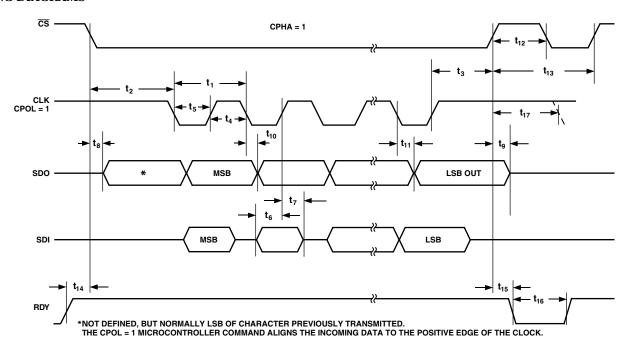

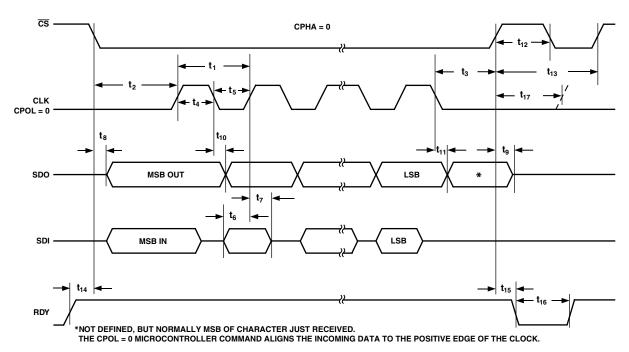

| INTERFACE TIMING CHARACTERI                                              | STICS (app         | ly to all parts) <sup>5, 11</sup>                            |     |                  |     |                  |

| Clock Cycle Time (t <sub>CYC</sub> )                                     | t <sub>1</sub>     |                                                              | 20  |                  |     | ns               |

| CS Setup Time                                                            | $t_2$              |                                                              | 10  |                  |     | ns               |

| CLK Shutdown Time to $\overline{CS}$ Rise                                | t <sub>3</sub>     |                                                              | 1   |                  |     | t <sub>CYC</sub> |

| Input Clock Pulsewidth                                                   | $t_4$ , $t_5$      | Clock Level High or Low                                      | 10  |                  |     | ns               |

| Data Setup Time                                                          | t <sub>6</sub>     | From Positive CLK Transition                                 | 5   |                  |     | ns               |

| Data Hold Time                                                           | t <sub>7</sub>     | From Positive CLK Transition                                 | 5   |                  |     | ns               |

| CS to SDO – SPI Line Acquire                                             | t <sub>8</sub>     |                                                              |     |                  | 40  | ns               |

| $\overline{\text{CS}}$ to SDO – SPI Line Release                         | t <sub>9</sub>     |                                                              |     |                  | 50  | ns               |

| CLK to SDO Propagation Delay <sup>12</sup>                               | t <sub>10</sub>    | $R_{\rm P} = 2.2 \text{ k}\Omega, C_{\rm L} < 20 \text{ pF}$ |     |                  | 50  | ns               |

| CS High Pulsewidth <sup>13</sup>                                         | t <sub>12</sub>    |                                                              | 10  |                  |     | ns               |

| $\overline{\text{CS}}$ High to $\overline{\text{CS}}$ High <sup>13</sup> | t <sub>13</sub>    |                                                              | 4   |                  |     | $t_{CYC}$        |

| RDY Rise to $\overline{CS}$ Fall                                         | t <sub>14</sub>    |                                                              | 0   |                  |     | ns               |

| CS Rise to RDY Fall Time                                                 | t <sub>15</sub>    |                                                              |     | 0.15             | 0.3 | ms               |

| Read/Store to Nonvolatile EEMEM <sup>14</sup>                            | t <sub>16</sub>    | Applies to Command $2_{\rm H}$ , $3_{\rm H}$ , $9_{\rm H}$   |     | 35               |     | ms               |

| CS Rise to Clock Edge Setup                                              | t <sub>17</sub>    |                                                              | 10  |                  |     | ns               |

| Preset Pulsewidth (Asynchronous)                                         | $t_{PRW}$          | Not Shown in Timing Diagram                                  | 50  |                  |     | ns               |

| Preset Response Time to Wiper Setting                                    | t <sub>PRESP</sub> | PR Pulsed Low to Refresh                                     |     | 140              |     | μs               |

|                                                                          |                    | Wiper Positions                                              |     |                  |     |                  |

| FLASH/EE MEMORY RELIABILITY                                              |                    |                                                              |     |                  |     |                  |

| Endurance <sup>15</sup>                                                  |                    |                                                              | 100 |                  |     | K Cycles         |

| Data Retention <sup>16</sup>                                             |                    |                                                              |     | 100              |     | Years            |

#### NOTES

Specifications subject to change without notice.

The ADN2850 contains 16,000 transistors. Die size: 93 mil  $\times$  103 mil, 10,197 sq mil.

REV. B –3–

<sup>&</sup>lt;sup>1</sup> Parts can be operated at 2.7 V single supply, except from 08C to -408C, where minimum 3 V is needed.

$<sup>^2</sup>$  Typicals represent average readings at 258C and  $V_{\rm DD}$  = 5 V.

<sup>&</sup>lt;sup>3</sup> Resistor position nonlinearity error R-INL is the deviation from an ideal value measured between the maximum resistance and the minimum resistance wiper positions.

R-DNL measures the relative step change from ideal between successive tap positions.  $I_W \sim 50 \mu A$  for  $V_{DD} = 2.7 \text{ V}$  and  $I_W \sim 400 \mu A$  for  $V_{DD} = 5 \text{ V}$ .

<sup>&</sup>lt;sup>4</sup> Resistor terminals W and B have no limitations on polarity with respect to each other.

<sup>&</sup>lt;sup>5</sup> Guaranteed by design and not subject to production test.

$<sup>^6</sup>$  Common-mode leakage current is a measure of the dc leakage from any terminal B and W to a common-mode bias level of  $V_{

m DD}/2$ .

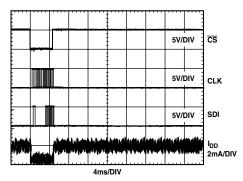

<sup>&</sup>lt;sup>7</sup> Transfer (XFR) mode current is not continuous. Current consumed while EEMEM locations are read and transferred to the RDAC register. See TPC 9.

$<sup>^{8}</sup>$   $P_{DISS}$  is calculated from (I\_DD  $\times$  V\_DD) + (I\_SS  $\times$  V\_SS).

<sup>&</sup>lt;sup>9</sup> Applies to photodiode of optical receiver.

$<sup>^{10}</sup>$  All dynamic characteristics use  $V_{\rm DD}$  = +2.5 V and  $V_{\rm SS}$  = -2.5 V.

$<sup>^{11}</sup>$  See timing diagram for location of measured values. All input control voltages are specified with  $t_R$  =  $t_F$  = 2.5 ns (10% to 90% of 3 V) and timed from a voltage level of 1.5 V. Switching characteristics are measured using both  $V_{\rm DD}$  = 3 V and 5 V.

$<sup>^{12}</sup>$ Propagation delay depends on value of  $V_{DD}$ ,  $R_{PULL\_UP}$ , and  $C_L$ . See Applications section.

<sup>&</sup>lt;sup>13</sup>Valid for commands that do not activate the RDY pin.

$<sup>^{14}</sup>$ RDY pin low only for commands 2, 3, 8, 9, 10, and PR hardware pulse: CMD\_8 ~ 1 ms; CMD\_9, 10 ~ 0.1 ms; CMD\_2, 3 ~ 20 ms. Device operation at  $T_A = -40$  °C and  $V_{DD} < 3$  V extends the save time to 35 ms.

<sup>15</sup> Endurance is qualified to 100,000 cycles as per JEDEC Std. 22 method A117 and measured at -40 °C, +25 °C, and +85 °C; typical endurance at +25 °C is 700,000 cycles.

<sup>&</sup>lt;sup>16</sup>Retention lifetime equivalent at junction temperature (T<sub>J</sub>) = 55°C as per JEDEC Std. 22, Method A117. Retention lifetime based on an activation energy of 0.6 V will derate with junction temperature.

#### **TIMING DIAGRAMS**

Figure 2a. CPHA = 1 Timing Diagram

Figure 2b. CPHA = 0 Timing Diagram

-4- REV. B

#### ABSOLUTE MAXIMUM RATINGS1

| 1200201211111111111100                                   |

|----------------------------------------------------------|

| $(T_A = 25^{\circ}C, \text{ unless otherwise noted.})$   |

| $V_{DD}$ to GND                                          |

| $V_{SS}$ to GND +0.3 V, -7 V                             |

| $V_{DD}$ to $V_{SS}$                                     |

| $V_B$ , $V_W$ to GND $V_{SS}$ – 0.3 V, $V_{DD}$ + 0.3 V  |

| $I_{\mathrm{B}},I_{\mathrm{W}}$                          |

| Intermittent <sup>2</sup> ±20 mA                         |

| Continuous ±2 mA                                         |

| Digital Inputs and Output Voltage                        |

| to GND                                                   |

| Operating Temperature Range <sup>3</sup> 40°C to +85°C   |

| Maximum Junction Temperature (T <sub>I MAX</sub> ) 150°C |

| Storage Temperature65°C to +150°C                        |

| Lead Temperature, Soldering <sup>4</sup>                 |

| Vapor Phase (60 sec)                                     |

| Infrared (15 sec) 220°C                                  |

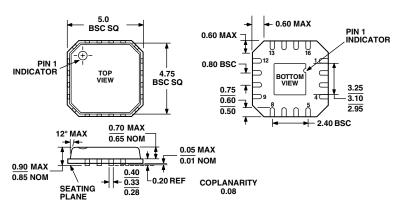

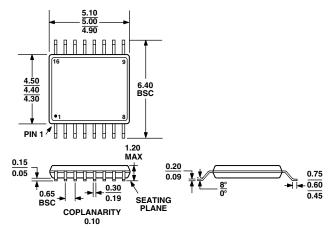

| Thermal Resistance Junction-to-Ambient $\theta_{JA}$ ,      |                        |

|-------------------------------------------------------------|------------------------|

| LFCSP-16                                                    | 35°C/W                 |

| TSSOP-16 1                                                  | 50°C/W                 |

| Thermal Resistance Junction-to-Case $\theta_{IC}$           |                        |

| TSSOP-16                                                    | $28^{\circ}\text{C/W}$ |

| Package Power Dissipation = $(T_{J MAX} - T_A)/\theta_{JA}$ |                        |

#### NOTES

<sup>1</sup>Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating; functional operation of the device at these or any other conditions above those listed in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ORDERING GUIDE**

| Model             | $R_{WB\_FS}$ $(k\Omega)$ | RDNL (LSB) | RINL<br>(LSB) | Temperature<br>Range (°C) | Package<br>Description | Package<br>Option | Ordering<br>Quantity | Top Mark* |

|-------------------|--------------------------|------------|---------------|---------------------------|------------------------|-------------------|----------------------|-----------|

| ADN2850BCP25      | 25                       | ±2         | ±4            | -40 to +85                | LFCSP-16               | CP-16             | 96                   | BCP25     |

| ADN2850BCP25-RL7  | 25                       | ±2         | ±4            | -40 to +85                | LFCSP-16               | CP-16             | 1,000                | BCP25     |

|                   |                          |            |               |                           | 7" Reel                |                   |                      |           |

| ADN2850BCP250     | 250                      | ±2         | ±4            | -40 to +85                | LFCSP-16               | CP-16             | 96                   | BCP250    |

| ADN2850BCP250-RL7 | 250                      | ±2         | ±4            | -40 to +85                | LFCSP-16               | CP-16             | 1,000                | BCP250    |

|                   |                          |            |               |                           | 7" Reel                |                   |                      |           |

| ADN2850BRU25      | 25                       | ±2         | ±4            | -40 to +85                | TSSOP-16               | RU-16             | 96                   | 2850B25   |

| ADN2850BRU25-RL7  | 25                       | ±2         | ±4            | -40 to +85                | TSSOP-16               | RU-16             | 1,000                | 2850B25   |

|                   |                          |            |               |                           | 7" Reel                |                   |                      |           |

<sup>\*</sup>Line 1 contains product number, ADN2850, line 2 Top Mark branding contains differentiating detail by part type, line 3 contains lot number, line 4 contains product date code YYWW.

#### CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the ADN2850 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

REV. B –5–

<sup>&</sup>lt;sup>2</sup>Maximum terminal current is bounded by the maximum current handling of the switches, maximum power dissipation of the package, and maximum applied voltage across any two of the B and W terminals at a given resistance.

<sup>&</sup>lt;sup>3</sup>Includes programming of nonvolatile memory.

<sup>&</sup>lt;sup>4</sup>Applicable to TSSOP-16 only. For LFCSP-16, please consult factory for details.

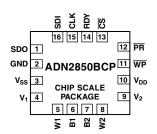

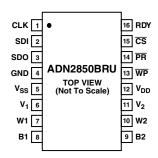

#### PIN CONFIGURATIONS

#### **ADN2850BCP PIN FUNCTION DESCRIPTIONS**

#### ADN2850BRU PIN FUNCTION DESCRIPTIONS

| Pin<br>No. | Mnemonic                   | Description                                                                                                                                                                                                                        | Pin<br>No. | Mnemonic                 | Description                                                                                                                                                                                                                               |

|------------|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | SDO                        | Serial Data Output Pin. Open-Drain output requires external pull-up resistor. CMD_9 and                                                                                                                                            | 1          | CLK                      | Serial Input Register Clock Pin. Shifts in one bit at a time on positive clock edges.                                                                                                                                                     |

|            |                            | CMD_10 activate the SDO output. See<br>Instruction Operation Truth Table (Table II).<br>Other commands shift out the previously                                                                                                    | 2          | SDI                      | Serial Data Input Pin. Shifts in one bit at a time on positive clock CLK edges.  MSB loaded first.                                                                                                                                        |

|            |                            | loaded SDI bit pattern delayed by 24 clock pulses. This allows daisy-chain operation of multiple packages.                                                                                                                         | 3          | SDO                      | Serial Data Output Pin. Open-drain out put requires external pull-up resistor. CMD_9 and CMD_10 activate the SDO output. See                                                                                                              |

| 2          | GND                        | Ground Pin, logic ground reference                                                                                                                                                                                                 |            |                          | Instruction Operation Truth Table (Table II).                                                                                                                                                                                             |

| 3          | V <sub>SS</sub>            | Negative Supply. Connect to zero volts for single-supply applications.                                                                                                                                                             |            |                          | Other commands shift out the previously loaded SDI bit pattern delayed by 24 clock                                                                                                                                                        |

| 4          | $V_1$                      | Log Output Voltage 1 generated from internal diode configured transistor                                                                                                                                                           |            |                          | pulses. This allows daisy-chain operation of multiple packages.                                                                                                                                                                           |

| 5          | W1                         | Wiper terminal of RDAC1 ADDR                                                                                                                                                                                                       | 4          | GND                      | Ground Pin, logic ground reference                                                                                                                                                                                                        |

| 6          | B1                         | $(RDAC1) = 0_H.$ B terminal of RDAC1                                                                                                                                                                                               | 5          | V <sub>SS</sub>          | Negative Supply. Connect to zero volts for single-supply applications.                                                                                                                                                                    |

| 7          | B2                         | B terminal of RDAC2                                                                                                                                                                                                                | 6          | $V_1$                    | Log Output Voltage 1 generated from internal                                                                                                                                                                                              |

| 8          | W2                         | Wiper terminal of RDAC2. ADDR $(RDAC2) = 1_{H}$ .                                                                                                                                                                                  | 7          | W1                       | diode configured transistor Wiper terminal of RDAC1. ADDR                                                                                                                                                                                 |

| 9          | $V_2$                      | Log Output Voltage 2 generated from internal diode configured transistor                                                                                                                                                           | 8          | B1                       | $(RDAC1) = 0_H.$ B terminal of RDAC1                                                                                                                                                                                                      |

| 10         | $V_{\mathrm{DD}}$          | Positive Power Supply Pin                                                                                                                                                                                                          | 9          | B2                       | B terminal of RDAC2                                                                                                                                                                                                                       |

| 11         | $\overline{\overline{WP}}$ | Write Protect Pin. When active low, WP prevents any changes to the present register                                                                                                                                                | 10         | W2                       | Wiper terminal of RDAC2. ADDR $(RDAC2) = 1_{H}$ .                                                                                                                                                                                         |

|            |                            | contents, except $\overline{PR}$ and CMD_1 and CMD_8 will refresh the RDAC register from EEMEM.                                                                                                                                    | 11         | $V_2$                    | Log Output Voltage 2 generated from internal diode configured transistor                                                                                                                                                                  |

|            |                            | Execute a NOP instruction before returning                                                                                                                                                                                         | 12         | $V_{ m DD}$              | Positive Power Supply Pin                                                                                                                                                                                                                 |

|            |                            | to WP high.                                                                                                                                                                                                                        | 13         | $\overline{\mathrm{WP}}$ | Write Protect Pin. When active low, WP prevents                                                                                                                                                                                           |

| 12         | PR                         | Hardware Override Preset Pin. Refreshes the scratch pad register with current contents of the EEMEM register. Factory default loads midscale 512 <sub>10</sub> until EEMEM loaded with a new value by the user (PR is activated at | 14         | PR                       | any changes to the present contents except $\overline{PR}$ and CMD_1 and CMD_8 will refresh the RDAC register from EEMEM. Execute a NOP instruction before returning to $\overline{WP}$ high. Hardware Override Preset Pin. Refreshes the |

| 13         | CS                         | the logic high transition).  Serial Register chip select active low.  Serial register operation takes place when   CS returns to logic high.                                                                                       |            |                          | scratch pad register with current contents of the EEMEM register. Factory default loads midscale $512_{10}$ until EEMEM loaded with a new value by the user $(\overline{PR})$ is activated at the                                         |

| 14         | RDY                        | Ready. Active high open-drain output. Identifies                                                                                                                                                                                   |            |                          | logic high transition).                                                                                                                                                                                                                   |

|            |                            | completion of commands 2, 3, 8, 9, 10, and $\overline{PR}$ .                                                                                                                                                                       | 15         | CS                       | Serial Register chip select active low. Serial                                                                                                                                                                                            |

| 15         | CLK                        | Serial Input Register Clock Pin. Shifts in one bit at a time on positive clock edges.                                                                                                                                              |            |                          | register operation takes place when $\overline{CS}$ returns to logic high.                                                                                                                                                                |

| 16         | SDI                        | Serial Data Input Pin. Shifts in one bit at a time on positive clock CLK edges. MSB loaded first.                                                                                                                                  | 16         | RDY                      | Ready. Active high open-drain output. Identifies completion of commands 2, 3, 8, 9, 10, and $\overline{PR}$ .                                                                                                                             |

-6- REV. B

Table I. 24-Bit Serial Data-Word

|       | MSB Instruction Byte 0 |    |    |    |    | Data Byte 1 |    |    |     |     |     | Data Byte 0 LSB |     |     |    | В  |    |    |    |      |            |    |      |                |

|-------|------------------------|----|----|----|----|-------------|----|----|-----|-----|-----|-----------------|-----|-----|----|----|----|----|----|------|------------|----|------|----------------|

| RDAC  | C3                     | C2 | C1 | C0 | 0  | 0           | 0  | A0 | X   | X   | X   | X               | X   | X   | D9 | D8 | D7 | D6 | D5 | D4 I | <b>)</b> 3 | D2 | D1 I | 00             |

| EEMEM | C3                     | C2 | C1 | C0 | A3 | A2          | A1 | A0 | D15 | D14 | D13 | D12             | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 I | )3         | D2 | D1 I | <del>)</del> 0 |

Command bits are C0 to C3. Address bits are A3-A0. Data bits D0 to D9 are applicable to RDAC wiper register whereas D0 to D15 are applicable to EEMEM Register. Command instruction codes are defined in Table II.

Table II. Instruction Operation Truth Table  $^{1, 2, 3}$

| Inst<br>Number  | l . | stru<br>3 • • |    |    | -  |      | ••• | B16 | Data Byte 1<br>B15 · · · · · B8 | Data Byte 0<br>B7 •••• B0     | Operation                                                                                                                                                                                            |

|-----------------|-----|---------------|----|----|----|------|-----|-----|---------------------------------|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                 | C3  | C2            | C1 | CO | A3 | 3 A2 | A1  | A0  | X • • • • D9 D8                 | D7 • • • • D0                 |                                                                                                                                                                                                      |

| 0               | 0   | 0             | 0  | 0  | X  | X    | X   | X   | $X \cdots X X$                  | X • • • • × X                 | NOP: Do nothing. See Table XI for Programming example.                                                                                                                                               |

| 1               | 0   | 0             | 0  | 1  | 0  | 0    | 0   | A0  | x····xx                         | X · · · · · X                 | Retrieve contents of EEMEM(A0) to RDAC(A0)<br>Register. This command leaves device in the Read<br>Program power state. To return part to the idle state,<br>perform NOP instruction 0. See Table XI. |

| 2               | 0   | 0             | 1  | 0  | 0  | 0    | 0   | A0  | $X \cdot \cdot \cdot \cdot X X$ | X • • • • • X                 | SAVE WIPER SETTING: Write contents of RDAC(A0) to EEMEM(A0). See Table X.                                                                                                                            |

| 3 <sup>4</sup>  | 0   | 0             | 1  | 1  | A3 | 8 A2 | A1  | A0  | D15 • • • • D8                  | D7 • • • • D0                 | Write contents of Serial Register Data Bytes 0 and 1 (total 16-bit) to EEMEM(ADDR). See Table XIII.                                                                                                  |

| 4 <sup>5</sup>  | 0   | 1             | 0  | 0  | 0  | 0    | 0   | A0  | $X \cdot \cdot \cdot \cdot X X$ | X • • • • X                   | Decrement 6 dB: Right shift contents of RDAC(A0) Register, stops at all "Zeros."                                                                                                                     |

| 5 <sup>5</sup>  | 0   | 1             | 0  | 1  | X  | X    | X   | X   | $X \cdot \cdot \cdot \cdot X X$ | $X \cdot \cdot \cdot \cdot X$ | Decrement All 6 dB: Right shift contents of all RDAC Registers, stops at all "Zeros."                                                                                                                |

| 6 <sup>5</sup>  | 0   | 1             | 1  | 0  | 0  | 0    | 0   | A0  | $X \cdot \cdot \cdot \cdot X X$ | X • • • • • X                 | Decrement contents of RDAC(A0) by "One," stops at all "Zeros."                                                                                                                                       |

| 7 <sup>5</sup>  | 0   | 1             | 1  | 1  | X  | X    | X   | X   | $X \cdot \cdot \cdot \cdot X X$ | $X \cdot \cdot \cdot \cdot X$ | Decrement contents of all RDAC Registers by "One," stops at all "Zeros."                                                                                                                             |

| 8               | 1   | 0             | 0  | 0  | X  | X    | X   | X   | $X \cdot \cdot \cdot \cdot X X$ | $X \cdot \cdot \cdot \cdot X$ | RESET: Load all RDACs with their corresponding EEMEM previously saved values.                                                                                                                        |

| 9               | 1   | 0             | 0  | 1  | A3 | 3 A2 | A1  | A0  | X····XX                         | x · · · · · x                 | Transfer contents of EEMEM (ADDR) to Serial Register Data Bytes 0 and 1, and previously stored data can be read out from the SDO pin. See Table XIV.                                                 |

| 10              | 1   | 0             | 1  | 0  | 0  | 0    | 0   | A0  | X····XX                         | x · · · · · x                 | Transfer contents of RDAC (A0) to Serial Register Data Bytes 0 and 1, and wiper setting can be read from the SDO pin. See Table XV.                                                                  |

| 11              | 1   | 0             | 1  | 1  | 0  | 0    | 0   | A0  | X • • • • D9 D8                 | D7 • • • • D0                 | Write contents of Serial Register Data Bytes 0 and 1 (total 11-bit) to RDAC(A0). See Table IX.                                                                                                       |

| 12 <sup>5</sup> | 1   | 1             | 0  | 0  | 0  | 0    | 0   | A0  | $X \cdot \cdot \cdot \cdot X X$ | X • • • • X                   | Increment 6 dB: Left shift contents of RDAC(A0), stops at all "Ones." See Table XII.                                                                                                                 |

| 13 <sup>5</sup> | 1   | 1             | 0  | 1  | X  | X    | X   | X   | $X \cdot \cdot \cdot \cdot X X$ | X · · · · · X                 | Increment All 6 dB: Left shift contents of all RDAC Registers, stops at all "Ones."                                                                                                                  |

| 14 <sup>5</sup> | 1   | 1             | 1  | 0  | 0  | 0    | 0   | A0  | $X \cdot \cdot \cdot \cdot X X$ | X • • • • × X                 | Increment contents of RDAC(A0) by "One," stops at all "Ones." See Table X.                                                                                                                           |

| 15 <sup>5</sup> | 1   | 1             | 1  | 1  | X  | X    | X   | X   | $X \cdot \cdot \cdot \cdot X X$ | X · · · · · X                 | Increment contents of all RDAC Registers by "One," stops at all "Ones."                                                                                                                              |

#### NOTES

REV. B -7-

<sup>&</sup>lt;sup>1</sup>The SDO output shifts out the last 24 bits of data clocked into the serial register for daisy-chain operation. Exception: for any instruction following Instruction 9 or 10, the selected internal register data will be present in data byte 0 and 1. The instructions following 9 and 10 must also be a full 24-bit data-word to completely clock out the contents of the serial register.

<sup>&</sup>lt;sup>2</sup>The RDAC register is a volatile scratch pad register that is refreshed at power ON from the corresponding nonvolatile EEMEM register.

<sup>&</sup>lt;sup>3</sup>Execution of the above operations takes place when the  $\overline{\text{CS}}$  strobe returns to logic high.

<sup>&</sup>lt;sup>4</sup>Instruction 3 writes 2 data bytes (total 16-bit) to EEMEM. But in the cases of addresses 0 and 1, only the last 10 bits are valid for wiper position setting.

<sup>&</sup>lt;sup>5</sup>The increment, decrement, and shift commands ignore the contents of the shift register data bytes 0 and 1.

#### **OPERATIONAL OVERVIEW**

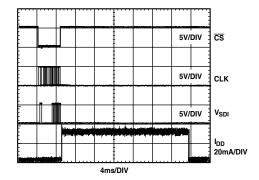

The ADN2850 programmable resistor is designed to operate as a true variable resistor. The resistor wiper position is determined by the RDAC register contents. The RDAC register acts as a scratch pad register which allows unlimited changes of resistance settings. The scratch pad register can be programmed with any position setting using the standard SPI serial interface by loading the 24-bit data-word. The format of the data-word is that the first 4 bits are instructions, the following 4 bits are addresses, and the last 16 bits are data. Once a specific value is set, this value can be saved into a corresponding EEMEM register. During subsequent power-ups, the wiper setting will automatically be loaded at that value. Saving data to the EEMEM takes about 25 ms and consumes approximately 20 mA. During this time the shift register is locked, preventing any changes from taking place. The RDY pin indicates the completion of this EEMEM saving process. There are also 13 two-bytes addresses, of user defined data that can be stored in EEMEM.

#### **OPERATION DETAIL**

There are 16 instructions that facilitate users' programming needs. Referring to Table II, the instructions are:

- 0. Do Nothing

- 1. Restore EEMEM setting to RDAC

- 2. Save RDAC setting to EEMEM

- 3. Save user data or RDAC setting to EEMEM

- 4. Decrement 6 dB

- 5. Decrement all 6 dB

- 6. Decrement one step

- 7. Decrement all one step

- 8. Reset all EEMEM settings to RDAC

- 9. Read EEMEM to SDO

- 10. Read Wiper Setting to SDO

- 11. Write data to RDAC

- 12. Increment 6 dB

- 13. Increment all 6 dB

- 14. Increment one step

- 15. Increment all one step

Tables VIII to XIV provide a few programming examples by using some of these instructions.

#### Scratch Pad and EEMEM Programming

The basic mode of setting the programmable resistor wiper position (programming the scratch pad register) is done by loading the serial data input register with the instruction 11, the corresponding address, and the data. Since the scratch pad register is a standard logic register, there is no restriction on the number of changes allowed. When the desired wiper position is determined, the user can load the serial data input register with the instruction 2, which stores the setting into the corresponding EEMEM register. The EEMEM value can be changed at any time or permanently protected by activating the  $\overline{\rm WP}$  command. Table III provides a programming example listing the sequence of serial data input (SDI) words and the corresponding serial data output (SDO) in hexadecimal format.

Table III. Set and Save RDAC with Independent Data to EEMEM Registers

| SDI                 | SDO                 | Action                                                                                                                      |

|---------------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------|

| B00100 <sub>H</sub> | XXXXXX <sub>H</sub> | Loads data 100 <sub>H</sub> into RDAC1 register,<br>Wiper W1 moves to 1/4 full-scale<br>position.                           |

| $20xxxx_H$          | $B00100_{H}$        | Saves copy of RDAC1 register content                                                                                        |

| B10200 <sub>H</sub> | 20xxxx <sub>H</sub> | into corresponding EEMEM1 register.<br>Loads 200 <sub>H</sub> data into RDAC2 register,<br>Wiper W2 moves to 1/2 full-scale |

| 21xxxx <sub>H</sub> | B10200 <sub>H</sub> | position. Saves copy of RDAC2 register contents into corresponding EEMEM2 register.                                         |

At system power ON, the scratch pad register is automatically refreshed with the value previously saved in the corresponding EEMEM register. The factory preset EEMEM value is midscale. During operations, the scratch pad register can also be refreshed with the current contents of the EEMEM registers in three different ways. First, executing instruction 1 retrieves the corresponding EEMEM value. Second, executing instruction 8 resets the EEMEM values of both channels. Finally, pulsing the  $\overline{PR}$  pin also refreshes both EEMEM settings. Operating the hardware control  $\overline{PR}$  function, however, requires a complete pulse signal. When  $\overline{PR}$  goes low, the internal logic sets the wiper at midscale. The EEMEM value will not be loaded until PR returns to high.

#### **EEMEM Protection**

The write-protect  $(\overline{WP})$  disables any changes of the scratch pad register contents regardless of the software commands, except that the EEMEM setting can be refreshed and can overwrite the  $\overline{WP}$  by using commands 1, 8, and  $\overline{PR}$  pulse. To disable  $\overline{WP}$ , it is recommended to execute a NOP command before returning  $\overline{WP}$  to logic high.

#### **Linear Increment and Decrement Commands**

The increment and decrement commands (14, 15, 6, 7) are useful for linear step adjustment applications. These commands simplify microcontroller software coding by allowing the controller to just send an increment or decrement command to the device. The adjustment can be individually or gang controlled. For increment command, executing instruction 14 will automatically move the wiper to the next resistance segment position. The master increment instruction 15 will move all resistor wipers up by one position.

#### Logarithmic Taper Mode Adjustment (±6 dB/step)

There are four programming instructions which provide the logarithmic taper increment and decrement wiper position control by either individual or gang control. 6 dB increment is activated by instructions 12 and 13 and 6 dB decrement is activated by instructions 4 and 5. For example, starting at zero scale, executing 11 times the increment instruction 12 will move the wiper in 6 dB per step from the 0% of the full-scale  $R_{WB}$  to the full-scale  $R_{WB}$ . The 6 dB increment instruction doubles the value of the RDAC register contents each time the command is executed. When the wiper position is near the maximum setting, the last 6 dB increment instruction will cause the wiper to go to the full-scale 1023-code position. Further 6 dB per increment instruction will no longer change the wiper position beyond its full-scale, Table IV.

6 dB step increment and decrement are achieved by shifting the bit internally to the left and right, respectively. The following information explains the nonideal ±6 dB step adjustment at certain

–8– REV. B

conditions. Table IV illustrates the operation of the shifting function on the individual RDAC register data bits. Each line going down the table represents a successive shift operation. Note that the left shift 12 and 13 commands were modified such that if the data in the RDAC register is equal to zero, and the data is left shifted, the RDAC register is then set to code 1. Similarly, if the data in the RDAC register is greater than or equal to midscale, and the data is left shifted, then the data in the RDAC register is automatically set to full scale. This makes the left shift function as ideal a logarithmic adjustment as possible.

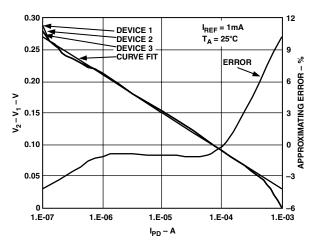

The right shift 4 and 5 commands will be ideal only if the LSB is zero (i.e., ideal logarithmic—no error). If the LSB is a one, then the right shift function generates a linear half LSB error, which translates to a number of bits-dependent logarithmic error as shown in Figure 3. The plot shows the error of the odd numbers of bits for ADN2850.

Table IV. Detail Left and Right Shift Functions for 6 dB Step Increment and Decrement

|                          | Left Shift                                                                                                                                                   | Right Shift                                                                                                                                    |                           |

|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|

| Left Shift<br>+6 dB/step | 00 0000 0000<br>00 0000 0001<br>00 0000 0110<br>00 0000 0100<br>00 0000 1000<br>00 0001 0000<br>00 0100 0000<br>00 1000 0000<br>01 0000 0000<br>11 1111 1111 | Right Shift  11 1111 1111 01 1111 1111 00 1111 1111 00 0111 1111 00 0001 1111 00 0000 1111 00 0000 0111 00 0000 0011 00 0000 0001 00 0000 0000 | Right Shift<br>-6 dB/step |

| <b>\</b>                 | 11 1111 1111                                                                                                                                                 | 00 0000 0000                                                                                                                                   | <b>+</b>                  |

Actual conformance to a logarithmic curve between the data contents in the RDAC register and the wiper position for each right shift 4 and 5 command execution contains an error only for odd numbers of bits. Even numbers of bits are ideal. The graph in Figure 3 shows plots of Log\_Error [i.e.,  $20 \times \log_{10}$  (error/code)] ADN2850. For example, code 3 Log\_Error =  $20 \times \log_{10}$  (0.5/3) = -15.56 dB, which is the worst case. The plot of Log\_Error is more significant at the lower codes.

Figure 3. Plot of Log\_Error Conformance for Odd Numbers of Bits Only (Even Numbers of Bits Are Ideal)

#### Using Additional Internal Nonvolatile EEMEM

The ADN2850 contains additional internal user storage registers (EEMEM) for saving constants and other 16-bit data. Table V provides an address map of the internal storage registers shown in the functional block diagram as EEMEM1, EEMEM2, and and 26 bytes (13 addresses  $\times$  2 bytes each) of USER EEMEM.

Table V. EEMEM Address Map

| EEMEM<br>Number | Address | EEMEM Content For        |

|-----------------|---------|--------------------------|

| 1               | 0000    | RDAC1 <sup>1, 2</sup>    |

| 2               | 0001    | RDAC2                    |

| 3               | 0010    | USER1 <sup>3</sup>       |

| 4               | 0011    | USER2                    |

| :               | :       | :                        |

| 15              | 1110    | USER13                   |

| 16              | 1111    | % Tolerance <sup>4</sup> |

#### NOTES

$^{1}$ RDAC data stored in EEMEM locations are transferred to their corresponding RDAC REGISTER at power-on, or when instructions 1, 8, and  $\overline{PR}$  are executed.

<sup>2</sup>Execution of instruction 1 leaves the device in the read mode power consumption state. After the last instruction 1 is executed, the user should perform a NOP, instruction 0 to return the device to the low power idling state.

<sup>3</sup>USER <data> are internal nonvolatile EEMEM registers available to store and retrieve constants and other 16-bit information using instructions 3 and 9 respectively. <sup>4</sup>Read only.

#### Calculating Actual Full-Scale Resistance

The actual tolerance of the rated full-scale resistance  $R_{WB1}$  is stored in EEMEM register 15 during factory testing. The actual full-scale resistance can therefore be calculated, which will be valuable for tolerance matching or calibration. Notice this value is read only, and the full-scale resistance of  $R_{WB2\_FS}$  matches  $R_{WB1\_FS}$  of typically 0.1%.

The tolerance in % is stored in the last 16 bits of data in EEMEM register 15. The format is sign magnitude binary format with the MSB designates for sign (0 = positive and 1 = negative), the next 7 MSB designate for the integer number, and the 8 LSB designate for the decimal number. See Table VI.

Table VI. Tolerance in % from Rated Full-Scale Resistance

For example, if  $R_{WB\_FS\_RATED}$  = 250 k $\Omega$  and the data is 0001 1100 0000 1111,  $R_{WB\_FS\_ACTUAL}$  can be calculated as follows:

MSB: 0 = Positive Next 7 MSB: 001 1100 = 28

8 LSB:  $0000\ 1111 = 15 \times 2^{-8} = 0.06$

% Tolerance = +28.06%

Thus,  $R_{WB\_FS\_ACTUAL} = 320.15 \text{ k}\Omega$

#### **Daisy-Chain Operation**

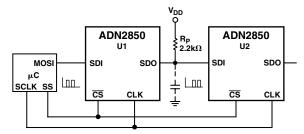

The serial data output pin (SDO) serves two purposes. It can be used to read out the contents of the wiper settings or EEMEM values using instructions 10 and 9 respectively. If these instructions are not used, SDO can be used for daisy-chaining multiple devices in simultaneous operations (see Figure 4). The SDO pin contains an open-drain N-Ch FET and requires a pull-up resistor if SDO function is used. Users need to tie the SDO pin of one package to the SDI pin of the next package. Users may need to increase the clock period because the pull-up resistor and the capacitive loading at the SDO-SDI interface may induce time delay to the subsequent devices (see Figure 4). If two ADN2850s are daisy-chained, a total 48 bits of data is required. The first 24 bits (formatted 4-bit instruction, 4-bit address, and 16-bit data) go to U2 and the second 24 bits with the same format go to U1. The  $\overline{\text{CS}}$  should be kept low until all 48 bits are clocked into their respective serial registers. The  $\overline{CS}$  is then pulled high to complete the operation.

Figure 4. Daisy-Chain Configuration

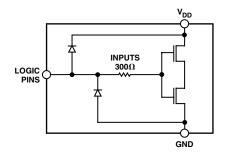

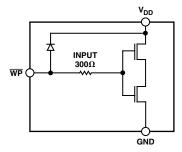

#### DIGITAL INPUT/OUTPUT CONFIGURATION

All digital inputs are ESD protected. Digital inputs are high impedance and can be driven directly from most digital sources. Active at logic low,  $\overline{PR}$  and  $\overline{WP}$  should be biased to  $V_{DD}$  if they are not used. There are no internal pull-up resistors present on any digital input pins. To avoid floating digital pins that may cause false triggering in a noisy environment, pull-up resistors should be added to these pins. However, this only applies to the case where the device will be detached from the driving source once it is programmed.

The SDO and RDY pins are open-drain digital outputs. Similarly, pull-up resistors are needed if these functions are used. To optimize the speed and power trade-off, use 2.2 k $\Omega$  pull-up resistors.

The equivalent serial data input and output logic is shown in Figure 5. The open-drain output SDO is disabled whenever chip select  $\overline{CS}$  is logic high. ESD protection of the digital inputs is shown in Figures 6a and 6b.

Figure 5. Equivalent Digital Input-Output Logic

Figure 6a. Equivalent ESD Digital Input Protection

Figure 6b. Equivalent WP Input Protection

#### **SERIAL DATA INTERFACE**

The ADN2850 contains a 4-wire, SPI compatible, digital interface (SDI, SDO,  $\overline{CS}$ , and CLK). The 24-bit serial word must be loaded with MSB first, and the format of the word is shown in Table I. The Command Bits (C0 to C3) control the operation of the programmable resistor according to the instruction shown in Table II. A0 to A3 are assigned for address bits. A0 is used to address RDAC1 or RDAC2. Addresses 2 to 14 are accessible by users. Address 15 is reserved for the factory. Table V provides an address map of the EEMEM locations. The data bits (D0 to D9) are the values that are loaded into the RDAC registers at instruction 11. The data bits (D0 to D15) are the values that are loaded into the EEMEM registers at instruction 3.

The last instruction prior to a period of no programming activity should be applied with the No Operation (NOP), instruction 0. It is recommended to do so to ensure minimum power consumption in the internal logic circuitry

The SPI interface can be used in two slave modes, CPHA = 1, CPOL = 1 and CPHA = 0, CPOL = 0. CPHA and CPOL refer to the control bits that dictate SPI timing in these microconverters and microprocessors: ADuC812/ADuC824, M68HC11, and MC68HC16R1/916R1.

-10- REV. B

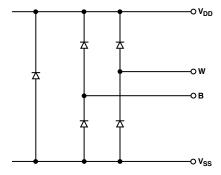

#### TERMINAL VOLTAGE OPERATING RANGE

The ADN2850 positive  $V_{DD}$  and negative  $V_{SS}$  power supply defines the boundary conditions for proper two-terminal programmable resistance operation. Supply signals present on terminals W and B that exceed  $V_{DD}$  or  $V_{SS}$  will be clamped by the internal forward biased diodes (see Figure 7).

Figure 7. Maximum Terminal Voltages Set by  $V_{DD}$  and  $V_{SS}$

The ground pin of the ADN2850 device is primarily used as a digital ground reference that needs to be tied to the PCB's common ground. The digital input control signals to the ADN2850 must be referenced to the device ground pin (GND), and satisfy the logic level defined in the Specifications table of this data sheet. An internal level shift circuit ensures that the common-mode voltage range of the two terminals extends from  $V_{SS}$  to  $V_{DD}$  regardless of the digital input level. In addition, there is no polarity constraint on voltage across terminals W and B. The magnitude of  $\left|V_{WB}\right|$  is bounded by  $V_{DD}-V_{SS}$ .

#### Power-Up Sequence

Since diodes limit the voltage compliance at terminals B and W (see Figure 7) it is important to power  $V_{DD}/V_{SS}$  first before applying any voltage to terminals B and W. Otherwise, the diode will be forward biased such that  $V_{DD}/V_{SS}$  will be powered unintentionally. For example, applying 5 V across  $V_{DD}$  will cause the  $V_{DD}$  terminal to exhibit 4.3 V. Although it is not destructive to the device, it may affect the rest of the user's system. As a result, the ideal power-up sequence is in the following order: GND,  $V_{DD}$ ,  $V_{SS}$ , Digital Inputs, and  $V_{B/W}$ . The order of powering  $V_{B}$ ,  $V_{W}$ , and Digital Inputs is not important as long as they are powered after  $V_{DD}/V_{SS}$ .

Regardless of the power-up sequence and the ramp rates of the power supplies, once  $V_{\rm DD}/V_{\rm SS}$  are powered, the power-on reset remains effective, which retrieves EEMEM saved values to the RDAC registers (see TPC 7).

#### Layout and Power Supply Bypassing

It is a good practice to employ compact, minimum-lead length layout design. The leads to the input should be as direct as possible with a minimum of conductor length. Ground paths should have low resistance and low inductance. To minimize the digital ground bounce, the digital signal ground reference can be joined remotely to the analog ground terminal of the ADN2850.

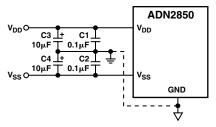

Similarly, it is also a good practice to bypass the power supplies with quality capacitors for optimum stability. Supply leads to the device should be bypassed with 0.01  $\mu F$  to 0.1  $\mu F$  disc or chip ceramics capacitors. Low ESR 1  $\mu F$  to 10  $\mu F$  tantalum or electrolytic capacitors should also be applied at the supplies to minimize any transient disturbance (see Figure 8).

Figure 8. Power Supply Bypassing

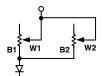

#### RDAC STRUCTURE

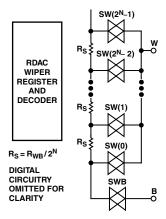

The patent-pending RDAC contains a string of equal resistor segments, with an array of analog switches, that act as the wiper connection. The number of positions is the resolution of the device. The ADN2850 has 1024 connection points, allowing it to provide better than 0.1% setability resolution. Figure 9 shows an equivalent structure of the connections between the two terminals that make up one channel of the RDAC. The  $S_{WB}$  will always be ON, while one of the switches SW(0) to  $SW(2^N-1)$  will be ON one at a time depending on the resistance position decoded from the data bits. Since the switch is not ideal, there is a 50  $\Omega$  wiper resistance,  $R_W$ . Wiper resistance is a function of supply voltage and temperature. The lower the supply voltage or the higher the temperature, the higher the resulting wiper resistance. Users should be aware of the wiper resistance dynamics if accurate prediction of the output resistance is needed.

Figure 9. Equivalent RDAC Structure

Table VII. Nominal Individual Segment Resistor Values

| Device Resolution | 25 kΩ | 250 kΩ |  |

|-------------------|-------|--------|--|

| 1024-Step         | 24.4  | 244    |  |

#### CALCULATING THE PROGRAMMABLE RESISTANCE

The nominal full-scale resistance of the RDAC between terminals W and B,  $R_{WB\_FS}$ , is available with 25 k $\Omega$  and 250 k $\Omega$  with 1024 positions (10-bit resolution). The final digits of the part number determine the nominal resistance value, e.g., 25 k $\Omega$  = 25 and 250 k $\Omega$  = 250.

The 10-bit data-word in the RDAC latch is decoded to select one of the 1024 possible settings. The following discussion describes the calculation of resistance  $R_{WB}(D)$  at different codes of a 25 k $\Omega$  part. The wiper's first connection starts at the B terminal for data  $000_H$ .  $R_{WB}(0)$  is 50  $\Omega$  because of the wiper resistance and it is independent of the full-scale resistance. The second connection is the first tap point where  $R_{WB}(1)$  becomes  $24.4~\Omega+50=74.4~\Omega$

REV. B –11–

for data  $001_H$ . The third connection is the next tap point representing  $R_{WB}(2) = 48.8 + 50 = 98.8 \,\Omega$  for data  $002_H$  and so on. Each LSB data value increase moves the wiper up the resistor ladder until the last tap point is reached at  $R_{WB}(1023) = 25026 \,\Omega$ . See Figure 9 for a simplified diagram of the equivalent RDAC circuit.

Figure 10. R<sub>WB</sub>(D) vs. Code

The general equation that determines the programmed output resistance between Wx and Bx is:

$$R_{WB}(D) = \frac{D}{1024} \times R_{WB_{-}FS} + R_{W}$$

(1)

where D is the decimal equivalent of the data contained in the RDAC register,  $R_{WB\_FS}$  is the full-scale resistance between terminals W and B, and  $R_W$  is the wiper resistance.

For example, the following output resistance values will be set for the following RDAC latch codes with  $V_{DD}$  = 5 V (applies to  $R_{WB\ FS}$  = 25 k $\Omega$  programmable resistors):

Table VIII.  $R_{WB}$  at Selected Codes ( $R_{WB\_FS} = 25 \text{ k}\Omega$ )

| D<br>(DEC)  | $R_{WB}(D)$ $(\Omega)$ | Output State                                   |

|-------------|------------------------|------------------------------------------------|

| 1023<br>512 | 25026<br>12550         | Full-Scale<br>Mid Scale                        |

| 1 0         | 74.4<br>50             | 1 LSB<br>Zero-Scale (Wiper contact resistance) |

Note that in the zero-scale condition a finite wiper resistance of 50  $\Omega$  is present. In this state, care should be taken to limit the current flow between W and B to no more than 20 mA to avoid degradation or possible destruction of the internal switches.

Channel-to-channel  $R_{WB}$  matching is well within 1% at full-scale. The change in  $R_{WB}$  with temperature has a 35 ppm/°C temperature coefficient.

–12– REV. B

## **Typical Performance Characteristics—ADN2850**

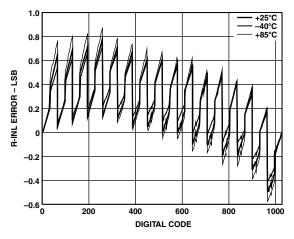

TPC 1. R-INL vs. Code,  $T_A = -40^{\circ}C$ ,  $+25^{\circ}C$ ,  $+85^{\circ}C$  Overlay,  $R_{AB} = 25 \text{ k}\Omega$

TPC 2. R-DNL vs. Code,  $T_A = -40$ °C, +25°C, +85°C Overlay,  $R_{AB} = 25 \text{ k}\Omega$

TPC 3.  $\Delta R_{WB}/\Delta T$  Rheostat Mode Tempco

TPC 4. Wiper On-Resistance vs. Code

TPC 5.  $I_{DD}$  vs. Temperature,  $R_{AB}$  = 25  $k\Omega$

TPC 6.  $I_{DD}$  vs. Clock Frequency,  $R_{AB}$  = 25  $k\Omega$

REV. B –13–

TPC 7. Memory Restore During Power-On Reset

TPC 8. I<sub>DD</sub> vs. Time (Save) Program Mode

SUPPLY CURRENT RETURNS TO MINIMUM POWER CONSUMPTION IF INSTRUCTION 0 (NOP) IS EXECUTED IMMEDIATELY AFTER INSTRUCTION 1 (READ EEMEM)

TPC 9. I<sub>DD</sub> vs. Time (Read) Program Mode

TPC 10. I<sub>WB\_MAX</sub> vs. Code

#### **TEST CIRCUITS**

Test Circuits 1 to 3 show some of the test conditions used in the Specifications table.

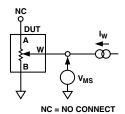

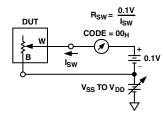

Test Circuit 1. Resistor Position Nonlinearity Error (Rheostat Operation; R-INL, R-DNL)

Test Circuit 2. Incremental ON Resistance

Test Circuit 3. Common-Mode Leakage Current

-14- REV. B

#### PROGRAMMING EXAMPLES

The following programming examples illustrate the typical sequence of events for various features of the ADN2850. Users should refer to Table II for the instructions and data-word format. The instruction numbers, addresses, and data appearing at SDI and SDO pins are displayed in hexadecimal format in the following examples.

Table IX. Scratch Pad Programming

| SDI                 | SDO                 | Action                                                                                                     |

|---------------------|---------------------|------------------------------------------------------------------------------------------------------------|

| B00100 <sub>H</sub> | XXXXXX <sub>H</sub> | Loads data 100 <sub>H</sub> into RDAC1 register,<br>Wiper W1 moves to 1/4 full-scale                       |

| B10200 <sub>H</sub> | B00100 <sub>H</sub> | position.<br>Loads data 200 <sub>H</sub> into RDAC2 register,<br>Wiper 2 moves to 1/2 full-scale position. |

Table X. Incrementing RDAC Followed by Storing the Wiper Setting to EEMEM

| SDI                 | SDO                 | Action                                                                                         |

|---------------------|---------------------|------------------------------------------------------------------------------------------------|

| B00100 <sub>H</sub> | XXXXXX <sub>H</sub> | Loads data 100 <sub>H</sub> into RDAC1 register,<br>Wiper W1 moves to 1/4 full-scale position. |

| $E0XXXX_H$          | B00100 <sub>H</sub> | Increments RDAC1 register by one to 101 <sub>H</sub> .                                         |

| $E0XXXX_H$          | E0XXXX <sub>H</sub> | Increments RDAC1 register by one to 102 <sub>H</sub> .                                         |

|                     |                     | Repeat the increment command -                                                                 |

|                     |                     | (E0XXXX <sub>H)</sub> until desired wiper                                                      |

|                     |                     | position is reached                                                                            |

| $20XXXX_H$          | XXXXXX              | Saves RDAC1 data into EEMEM1                                                                   |

|                     |                     | Optionally tie WP to GND to protect EEMEM values                                               |

Table XI. Restoring EEMEM Values to RDAC Registers

EEMEM values for RDACs can be restored by: Power-On, Strobing  $\overline{PR}$  pin or Programming shown below.